## Circuiti Combinatori Notevoli

#### Corrado Santoro

### Corso di Architettura degli Elaboratori

## 1 Il Multiplexer

Un multiplexer "K-a-1" è una rete logica che possiede:

- $K = 2^n$  input dati  $x_0, x_1, ..., x_{K-1}$ ;

- *n* input di controllo;

- una singola uscita.

L'obiettivo del multiplexer è quello di "connettere" uno solo degli ingressi  $x_i$  all'uscita sulla base degli n bit di controllo: detto S il valore (decimale) rappresentato dagli n bit, allora il valore dell'ingresso  $x_S$  verrà copiato sull'uscita, mentre tutti gli altri ingressi verranno ignorati.

La tabella della verità di un multiplexer 4-a-1 è la seguente:

| $x_0$ | $x_1$ | $x_2$ | $x_3$ | $c_1$ | $c_0$ | $\mid y \mid$ |

|-------|-------|-------|-------|-------|-------|---------------|

| 0     | X     | X     | X     | 0     | 0     | 0             |

| 1     | X     | X     | X     | 0     | 0     | 1             |

| X     | 0     | X     | X     | 0     | 1     | 0             |

| X     | 1     | X     | X     | 0     | 1     | 1             |

| X     | X     | 0     | X     | 1     | 0     | 0             |

| X     | X     | 1     | X     | 1     | 0     | 1             |

| X     | X     | X     | 0     | 1     | 1     | 0             |

| X     | X     | X     | 1     | 1     | 1     | 1             |

Nella tabella, il valore "X" rappresenta lo stato di "don't care": significa che l'uscita è indipendente dal valore della relativa variable che dunque può assumere qualunque valore; questo implica che, nella sintesi della funzione logica, le variabili contrassegnate come "don't care" possono essere ignorate dato che esse non hanno effetto in quel caso specifico. La funzione logica che rappresenta il comportamento del multiplexer 4-a-1 è dunque la seguente:

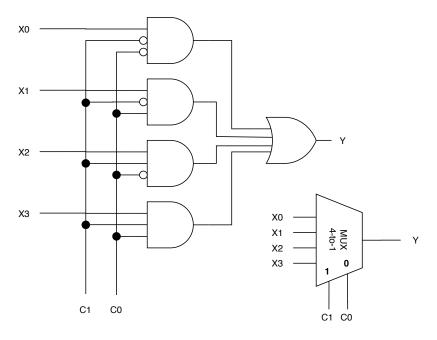

$$y = x_0\overline{c_1}\overline{c_0} + x_1\overline{c_1}c_0 + x_2c_1\overline{c_0} + x_3c_1c_0$$

Essa è derivata andando a considerare i casi cui in l'uscita vale 1, ed omettendo, nel prodotto risultante, tutte le varibili "don't care".

La rete logica risultante è riportata nella figura seguente, la quale mostra anche (in basso a destra) il simbolo che di solito si utilizza per rappresentare, in un circuito elettrico, il multiplexer.

# 2 L'Encoder a priorità

Un **Encoder a priorità** K-to-n è una rete logica dotata di:

- $K = 2^n$  input  $x_0, x_1, ..., x_{K-1}$ ;

- n output  $y_{n-1}, ..., y_0$ .

Il comportamento base consiste nel generare, sulle uscite, il *pattern binario* che rappresenta il *numero dell'ingresso* che si trova a stato logico 1; qualora più di un ingresso si trovi allo stato logico 1 in genere si dà priorità all'ingresso di ordine più basso.

La tabella di verità di un encoder 8-to-3 con priorità è la seguente:

| $x_0$ | $x_1$ | $x_2$ | $x_3$ | $x_4$ | $x_5$ | $x_6$ | $x_7$                 | $y_2$ | $y_1$ | $y_0$ |

|-------|-------|-------|-------|-------|-------|-------|-----------------------|-------|-------|-------|

| 1     | X     | X     | X     | X     | X     | X     | X                     | 0     | 0     | 0     |

| 0     | 1     | X     | X     | X     | X     | X     | X                     | 0     | 0     | 1     |

| 0     | 0     | 1     | X     | X     | X     | X     | X                     | 0     | 1     | 0     |

| 0     | 0     | 0     | 1     | X     | X     | X     | X                     | 0     | 1     | 1     |

| 0     | 0     | 0     | 0     | 1     | X     | X     | X<br>X<br>X<br>X<br>X | 1     | 0     | 0     |

| 0     | 0     | 0     | 0     | 0     | 1     | X     | X                     | 1     | 0     | 1     |

| 0     | 0     | 0     | 0     | 0     | 0     | 1     | X                     | 1     | 1     | 0     |

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1                     | 1     | 1     | 1     |

Nella tabella, il valore "X" rappresenta lo stato di "don't care".

#### 3 Il Decoder

Un **Decoder** n-to-K è una rete logica dotata di:

- $n \text{ input } x_{n-1}, ..., x_0;$

- $K = 2^n$  output  $y_0, y_1, ..., y_{K-1}$ .

Il comportamento è inverso rispetto a quello dell'encoder, il decoder infatti attiva l'uscita  $y_i$  posto che gli ingressi formino il *pattern binario* che rappresenta giusto il valore i. In genere è presente anche un ingresso di Enable che "attiva" il funzionamento specificato, ossia se Enable=0, tutte le uscite sono allo stato logico 0 indipendentemente dal valore degli ingressi  $x_i$ .

La tabella di verità di un decoder 3-to-8 è la seguente:

| Enable | $x_2$ | $x_1$ | $x_0$ | $y_0$ | $y_1$ | $y_2$ | $y_3$ | $y_4$ | $y_5$ | $y_6$ | $y_7$ |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0      | X     | X     | X     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 1      | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 1      | 0     | 0     | 1     | 0     | 1     | 0     | 0     | 0     | 0     | 0     | 0     |

| 1      | 0     | 1     | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 0     | 0     |

| 1      | 0     | 1     | 1     | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 0     |

| 1      | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     |

| 1      | 1     | 0     | 1     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     |

| 1      | 1     | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     |

| 1      | 1     | 1     | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     |

Nella tabella, il valore "X" rappresenta lo stato di "don't care". Le funzioni logiche delle uscite sono le seguenti:

$y_0 = Enable \overline{x_2} \overline{x_1} \overline{x_0}$

$y_1 = Enable \overline{x_2} \overline{x_1} x_0$

$y_2 = Enable \overline{x_2} x_1 \overline{x_0}$

$y_3 = Enable \overline{x_2} x_1 x_0$

$y_4 = Enable x_2 \overline{x_1} \overline{x_0}$

$y_5 = Enable x_2 \overline{x_1} x_0$

$y_6 = Enable x_2 x_1 \overline{x_0}$

$y_7 = Enable x_2 x_1 x_0$