Bus Sincroni Animator

|

Scopo di questa pagina e dell'animazione contenuta č quello di permettere una migliore comprensione (si spera) della sottosezione 3.4.4 del testo Tanembaun "ARCHITETTURA DEI COMPUTER". |

N.B.: Questa pagina deve essere utilizzata come supporto per lo studio della sottosezione 3.4.4 del testo, non alternativamente al testo.

|

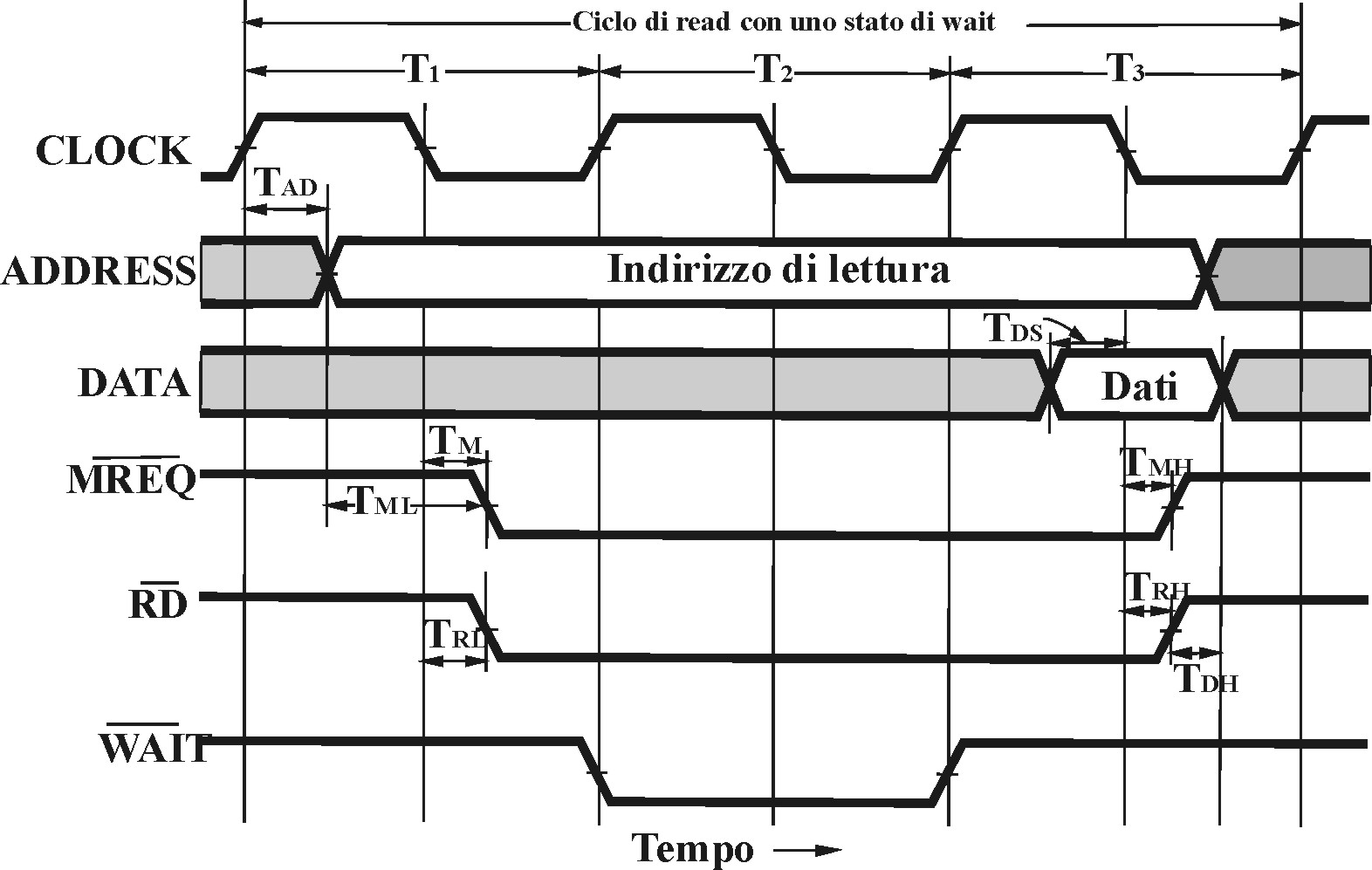

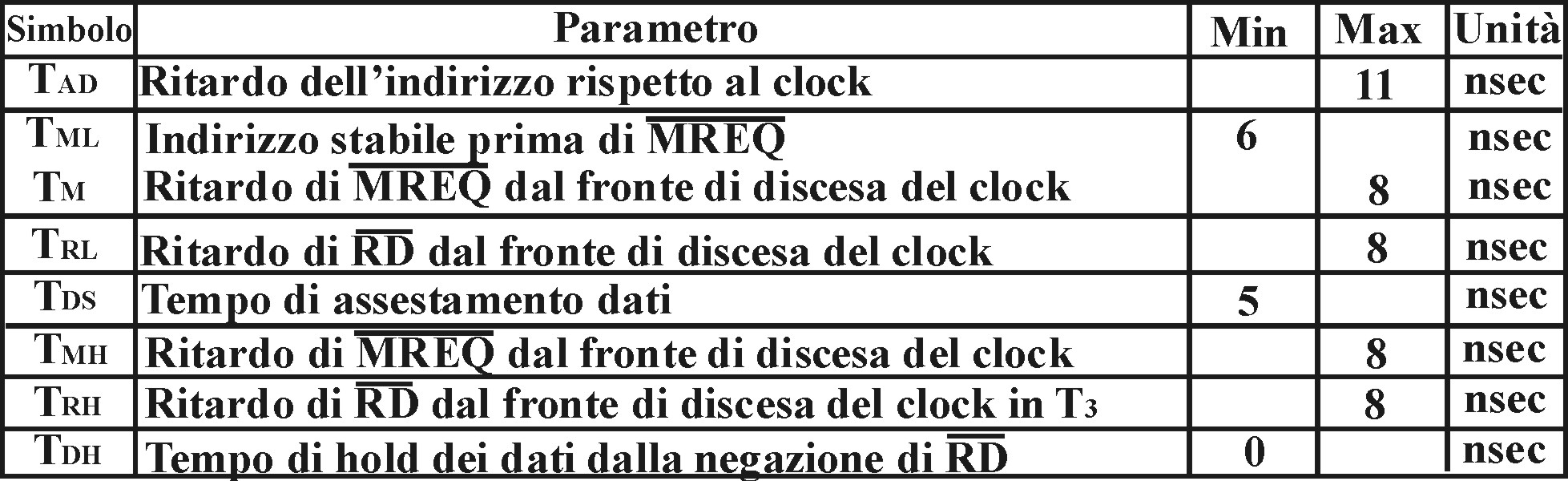

Un bus sincrono ha una linea pilotata da un oscillatore.

Il segnale su questa linea consiste in un'onda quadrata con frequenza solitamente fra 5MHz e 100MHz. Tutte le attivitŕ del bus richiedono

un numero intero di questi cicli, chiamati cicli del bus.

|

|

Fig.1 |

|

Fig.2 |

|

Animazione di un ciclo di lettura in memoria da parte della CPU. |