Specifiche hardware PCI

Lo standard PCI

↑

Il Periferal Component Interconnection è un

bus che ricopre un ruolo molto importante nell'architettura dei moderni

computer.

Esistono diverse versioni dello standard, le principali sono:

-

Conventional PCI − il primo standard. La velocità

massima supportata è 33 MHz che, con parole di 32bits, si traduce

in 33*4byte = 133 MB/s.

-

PCI 2.2 − aggiunge il supporto a dati a 64bits e lavora a 66 MHz,

con un trasfer rate massima di 66*8bytes=528 MB/s.

-

PCI Express − rappresenta in realtà uno standard completamente

nuovo, nato per permettere il trasferimento veloce verso dispositivi

quali le schede video, andando a sostituire l'interfaccia AGP.

Supporta velocità da 133MHz a 533MHz.

Interconnessioni

↑

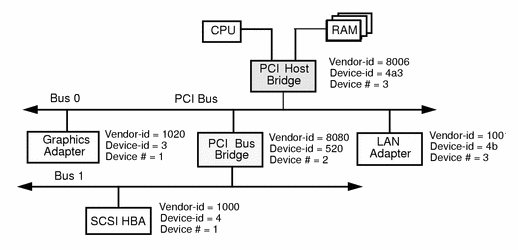

Il bus PCI è un bus esterno alla CPU, presente sulla scheda

madre. Lo schema in figura mostra come il PCI si interfaccia, tramite i

bridge, alle altre periferiche e bus di sistema. Il

Southbridge, un ponte di collegamento per dispositivi

più lenti è in grado di collegare il PCI ad altri bus

ausiliari quali:

Il bus PCI è un bus esterno alla CPU, presente sulla scheda

madre. Lo schema in figura mostra come il PCI si interfaccia, tramite i

bridge, alle altre periferiche e bus di sistema. Il

Southbridge, un ponte di collegamento per dispositivi

più lenti è in grado di collegare il PCI ad altri bus

ausiliari quali:

- USB

- Real Time Clock

- ISA, bus in uso prima di PCI, mantenuto solo per compatibilità

- IDE, ovvero P-ATA e S-ATA

- BIOS

Il Northbridge, invece, svolge l'importante ruolo di dirigere il

flusso dati verso la memoria o verso i bus esterni. Questo avviene

programmando i suoi registri interni indicando a quale range di

indirizzi risponde la memoria.

Tramite il Northbridge, il bus PCI è infatti indirettamente collegato

al bus di sistema − Front Side Bus −

alla memoria e anche all'eventuale bus PCI-E o AGP. Ogni bus PCI

supporta fino a 2^5=32 dispositivi collegati. E' però

possibile collegare bus aggiuntivi tramite i PCI-to-PCI Bridge.

Il bus PCI funziona con 32 linee denominate AD[31:0], che vengono

multiplexate per fornire prima i bit indirizzi, poi quelli dati.

L'ordine dei bit fissato è Little Endian, il che significa

che le architetture big endian devono, tramite software, effettuare la

conversione di formato.

Attivazione dispositivo

↑

All'avvio del sistema, i dispositivi pci non hanno ancora un indirizzo

assegnato. Per permettere la loro configurazione, in tale contesto, si

utilizza un segnale particolare chiamato IDSEL#. Per ogni

slot

del bus il pin IDSEL# viene normalmente collegato ad una diversa linea

di indirizzo, tra AD31 e AD11, in modo che il segnale di selezione sia

attivo, per ognuno dei possibili 21 dispositivi, su una linea

d'indirizzo differente. Le restanti 11 linee AD10-0 sono invece

decodificate dal dispositivo selezionato in base ai corrispettivi bit

del codice BDF.

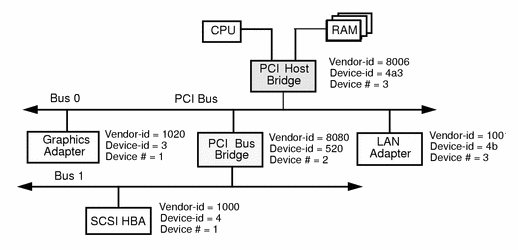

Il PCI Host Bridge è il dispositivo che si occupa di decodificare

l'indirizzo BDF, permettendo la configurazione dei dispositivi all'avvio

del sistema. Il PCI Host Bridge mette in collegamento il bus PCI con il

bus di sistema e, normalmente, risponde agli indirizzi di I/O

0xCF8 e 0xCFC. La scrittura sulla prima porta,

attiva la linea IDSEL# del dispositivo e, contemporaneamente, seleziona

la funzione da configurare. La seconda viene invece usata per

l'effettivo scambio dati.

Il PCI Host Bridge normalmente è integrato all'interno del Northbridge.

Numero di dispositivi

↑

Il codice BDF ha un campo di 5 bit per la specifica di 2^5=32

dispositivi diversi da configurare ma l'IDSEL# può essere decodificato

in sole 21 linee. Questo è un primo limite sul numero di dispositivi

teorici su ciascun bus.

L'effettivo limite fisico del bus è ancora inferiore; non più di

10 dispositivi con requisiti base possono essere collegati

al bus. Se poi si aumenta in frequenza, il limite si abbassa

ulteriormente a circa 4. Utilizzare bus multipli tramite dei

bridges risulta quindi una scelta necessaria (si veda

http://www.pcisig.com/reflector/msg05272.html)

Home

<

Prev

|

Next

>

Il bus PCI è un bus esterno alla CPU, presente sulla scheda

madre. Lo schema in figura mostra come il PCI si interfaccia, tramite i

bridge, alle altre periferiche e bus di sistema. Il

Southbridge, un ponte di collegamento per dispositivi

più lenti è in grado di collegare il PCI ad altri bus

ausiliari quali:

Il bus PCI è un bus esterno alla CPU, presente sulla scheda

madre. Lo schema in figura mostra come il PCI si interfaccia, tramite i

bridge, alle altre periferiche e bus di sistema. Il

Southbridge, un ponte di collegamento per dispositivi

più lenti è in grado di collegare il PCI ad altri bus

ausiliari quali: