# Component development on FPGA

Tutorial 09 on Dedicated systems

Teacher: Giuseppe Scollo

University of Catania Department of Mathematics and Computer Science Graduate Course in Computer Science, 2019-20

DMI - Graduate Course in Computer Science

Copyleft @ 2020 Giuseppe Scollo

1 di 7

## Table of Contents

- 1. Component development on FPGA. Planning of student seminars

- 2. tutorial outline

- 3. introduction to the Qsys software tool

- 4. example of a Nios II system integration on FPGA

- 5. development of an Avalon memory-mapped component on FPGA

- 6. references

DMI - Graduate Course in Computer Science

DMI - Graduate Course in Computer Science

Copyleft @ 2020 Giuseppe Scollo

### 3 di 7

# introduction to the Qsys software tool

development of a SoC with applications is a typical HW/SW codesign activity

it consists of design and development of components of both kinds, as well as their

integration to form a single system

the Quartus tool utilized in this lab tutorial for the integration of hardware components in SoC development is  $\varphi_{sys}$

it enables one to select components such as processors, memories, I/O interfaces, timers, custom hardware components etc., in a GUI where their connections may be specified, and then to automatically generate the hardware description of the system

the subsequent compilation in Quartus produces a system for the programming of the FPGA, whereupon one may load a software application by means of the Monitor Program, compile it and execute it under control of the GDB debugger, as shown in the previous lab tutorial in this lab tutorial two simple Qsys design cases are shown:

- construction of a Nios II system and execution of an application that handles two FPGA peripherals (switches and LED's)

- construction of a custom hardware component (a register) and its integration in a Nios II system through a memory-mapped slave interface on the Avalon bus, where its content is visualized on seven-segment displays

DMI - Graduate Course in Computer Science

#### example of a Nios II system integration on FPGA

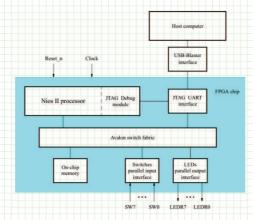

the first part of the classroom lab reproduces the execution of the example of Qsys construction of a Nios II system equipped with a small amount of on-chip memory and a couple of memory-mapped I/O peripherals with Avalon bus interfaces, as shown in the figure, described in the first reference tutorial

the VHDL and software sources are available in the reserved lab area, as archive <code>qsys\_tutorial.zip</code>, in folder VHDL/code/e09 <code>classroom</code>

Figure 1. Block diagram of a simple example of Nios II system on FPGA

DMI - Graduate Course in Computer Science

Copyleft @ 2020 Giuseppe Scollo

5 di 7

### development of an Avalon memory-mapped component on FPGA

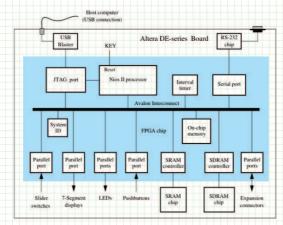

the second part of the classroom lab reproduces the execution of the example of construction of a Qsys system equipped with a memory-mapped custom hardware component with an Avalon bus interface, as shown in the figure, described in the second reference tutorial

the VHDL sources are available in the reserved lab area, as archive component\_tutorial.zip, in folder VHDL/code/e09 classroom

Figure 2. Block diagram of a complex example of Nios II system on FPGA

DMI - Graduate Course in Computer Science

DMI - Graduate Course in Computer Science