# Combinational network examples in VHDL

Tutorial 04 on Dedicated systems

Teacher: Giuseppe Scollo

University of Catania Department of Mathematics and Computer Science Graduate Course in Computer Science, 2018-19

DMI - Graduate Course in Computer Science

Copyleft @ 2019 Giuseppe Scollo

1 di 12

# Table of Contents

- 1. Combinational network examples in VHDL

- 2. tutorial outline

- 3. tri-state buffers

- 4. decoders

- 5. 7-segment display decoders

- 6. multiplexers

- 7. ALU functions

- 8. lab experience

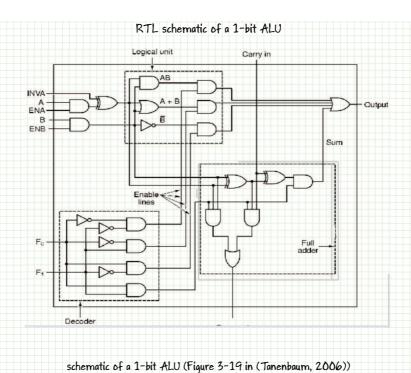

- 9. RTL schematic of a 1-bit ALU

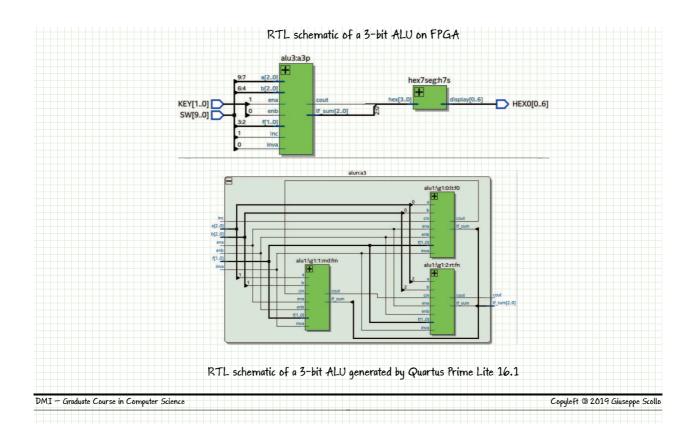

- 10. RTL schematic of a 3-bit ALU on FPGA

- 11. references

DMI - Graduate Course in Computer Science

Copyleft @ 2019 Giuseppe Scollo

## tutorial outline

this tutorial deals with VHDL descriptions of frequently used hardware components:

- > tri-state buffers

- > decoders:

- > n-input decoders

- > 7-segment display decoders

- > multiplexers

- ALU functions

various aspects and constructs of the VHDL language are introduced in the context of the proposed examples

furthermore, a lab experience is proposed which collects various aspects of VHDL that are illustrated by the examples presented here, and where some of these components may be reused for the implementation of the proposed experiment

DMI — Graduate Course in Computer Science

Copyleft @ 2019 Giuseppe Scollo

3 di 12

# tri-state buffers

the standard, two-valued boolean type BIT, does not suffice to represent all situations that may come into play in circuit design

e.g. a circuit line may need be disconnected dynamically, in order to allow bus access by multiple drivers, one at a time

tri-state buffer

tri-state gates are typically utilized to this purpose

the IEEE 1164 standard defines the nine-valued std\_ulogic type:

'U' Uninitialized

K' Forcing unknown

'O' Forcing O

'1' Forcing 1

'Z' High impedance

'W' Weak unknown

"L" Weak O

'H' Weak 1

'-' Don't care

yet std\_ulogic does not allow multiple driver access to the same line

its subtype std logic is endowed with a resolution function to resolve the

contention, which is allowed thus

|   | U | X | 0 | 1 | Z | W | L | н | - |

|---|---|---|---|---|---|---|---|---|---|

| U | U | U | U |   | U | U |   | U | U |

| X | U | X | X | X | X | X | X | X | X |

| 0 | U | X | 0 | X | 0 | 0 | 0 | 0 | X |

| 1 | U | X | X | 1 | 1 | 1 | 1 | 1 | X |

| Z | U | X | 0 | 1 | Z | W | L | H | X |

| W | U | X | 0 | 1 | W | W | W | W | X |

| L | U | X | 0 | 1 | L | W | L | W | X |

| H | U | X | 0 | 1 | H | W | W | H | X |

| - | U | X | X | X | X | X | X | X | X |

contention resolution between values of type std\_logic

library ieee; use ieee.std\_logic\_1164.all; entity tri\_state is

port (x, en : in std\_logic; y : out std\_logic);

end entity tri\_state; architecture when\_else of tri\_state is begin

y <= x when en = '1' else 'Z'; end architecture when\_else;

DMI - Graduate Course in Computer Science

Copyleft 3 2019 Giuseppe Scollo

5 di 12

```

7-segment display decoders

familiar device of daily use ...

a decoder for a seven-segment display converts a 4-bit input to the 7-bit configuration of the display

segment states that visualizes the character corrisponding to the (hex or decimal) digit which has the value

coded by the input

library ieee;

the following example (taken from Zwoliński, Sect.

use ieee.std_logic_1164.all;

4.2.3)

entity seven_seg is port (a : in std_logic_vector(3 downto 0);

visualizes decimal digits

z : out std_logic_vector(6 downto 0));

visualizes E if the input value is ≥ 10

end entity seven seg;

in all other cases the display is blanked

architecture with_select of seven_seg is

begin

with a select

1010 Others

end architecture with_select;

Zwoliński, Figure 4.3 - Seven-segment display

Copyleft @ 2019 Giuseppe Scollo

```

DMI - Graduate Course in Computer Science

#### multiplexers architecture sequential of wide or is VHDL description of a description of an n-input OR gate: multiplexer with a single select beain process (x) is library ieee: input: variable z : std\_logic; use ieee.std\_logic\_1164.all; begin z := x(0);entity wide\_or is generic (n : POSITIVE); library ieee; use ieee.std\_logic\_1164.all; if n > 1 then port ( for i in 1 to n-1 loop in std\_logic\_vector(n-1 downto 0); entity mux1 is z := x(i) or z;y : out std logic); port ( s : in std\_logic; end loop; end entity wide\_or; end if: a : in std\_logic; b : in std\_logic; y <= z; end process: y : out std\_logic end architecture sequential; n-select input multiplexer end entity mux1; library ieee; architecture structural of mux is signal decout : std\_logic\_vector(2\*\*n-1 downto 0); signal andout : std\_logic\_vector(2\*\*n-1 downto 0); use ieee.std\_logic\_1164.all; entity mux is architecture basic of mux1 is generic (n : POSITIVE := 1); port ( begin di: entity WORK.decoder generic map (n) y <= a when s = '0' else b when s = '1' else s: in std\_logic\_vector(n-1 downto 0); a: in std\_logic\_vector(2\*\*n-1 downto 0); port map (a => s, z => decout); oi: entity WORK.wide\_or generic map (2\*\*n) end architecture basic; port map (x => andout, y => z); andout <= a and decout; z : out std\_logic); end entity mux end architecture structural: instantiation of the generic multiplexer library ieee; use ieee.std\_logic\_1164.all; architecture instance of mux2 is di: entity WORK.mux generic map (2) entity mux2 is multiplexer with a 2-select input port map (s, a, z); s:in std\_logic\_vector(1 downto 0); a:in std\_logic\_vector(3 downto 0); z:out std\_logic); end architecture instance how to generalize to n-select input? end entity mux2; DMI - Graduate Course in Computer Science Copyleft 3 2019 Giuseppe Scollo

7 di 12

```

ALU functions

an ALU is a multifunction unit: a control input selects the operation to be executed

function

00

Q \le A \text{ or } B

an example of multifunction logic unit has the selection as specified in the table

01

Q \le A and B

and may be described in VHDL as follows:

10

Q \le not B

library ieee;

11

O \le A \text{ xor } B

architecture with select of alu logic is

use ieee.std_logic_1164.all;

constant undefined : std_logic_vector(n-1 downto 0) := (others => 'X');

entity alu_logic is

generic ( n : POSITIVE := 16 );

begin

with s select

port (

q <= a or b when "00"

a and b when "01",

a: in std_logic_vector((n-1) downto 0);

b : in std_logic_vector((n-1) downto 0);

s : in std_logic_vector(1 downto 0);

not b; when "10" a xor b when "11",

q : out std_logic_vector((n-1) downto 0)

undefined when others;

end architecture with_select;

end entity alu_logic;

for operands wider than one bit, ALU's arithmetic function may be specified in either structural

or functional style; the latter as follows

architecture sequential of adder is

begin

process(a,b,ci)

use IEEE.std_logic_1164.all;

entity adder is

variable carry : std_logic;

generic(n-1 : POSITIVE := 16);

variable psum : std_logic_vector(n-1 downto 0);

port (

a : in std_logic_vector (n-1 downto 0);

begin

carry := ci;

b : in std_logic_vector (n-1 downto 0);

ci : in std_logic;

for i in 0 to n-1 loop

psum(i) := a(i) xor b(i) xor carry;

sum : out std_logic_vector (n-1 downto 0);

carry := (a(i) and b(i)) or (((a(i) xor b(i)) and carry);

co : out std_logic

end loop;

sum <= psum;

co <= carry;

end entity adder;

1-bit full-adder

end process;

```

DMI - Graduate Course in Computer Science

end architecture sequential;

8 di 12

Copyleft @ 2019 Giuseppe Scollo

### lab experience

the 8-bit ALU simulator implemented by S. Lentini and G. Nicotra illustrates how one can iteratively construct the 8-bit ALU by suitably composing 1-bit ALU stages

the schematic and an animated illustration of the ALU functions are presented in the "Arithmetic logic unit" part of the Flash animation of that project

using the VHDL constructs seen in the examples through this tutorial:

- build a VHDL model of the 1-bit ALU; an equivalent solution to that which is represented by the schematic reproduced next, may be obtained by appropriate use of a multiplexer in place of a decoder

- building on this result, construct a generic model of the n-bit ALU

- 3. compose a 3-bit instance of the generic ALU model with a VHDL model of the hex to 7-segment display decoder (available in the reserved lab area), mapping the I/O ports of the obtained model to pins of the DE1-SoC FPGA, as specified next and further illustrated in the subsequent RTL schematic

- 4. program the FPGA by using its 10 switches and 2 keys for the ALU input (the 2 keys for the ENA, ENB inputs, 6 switches for the A, B operands, the remaining switches for the other control inputs) and a 7-segment display for the visualization of the result (carry included, for addition)

- 5. test the functioning of the 3-bit ALU on the FPGA by acting on the switches and assigned keys

DMI - Graduate Course in Computer Science

Copyleft @ 2019 Giuseppe Scoll

9 di 12

DMI - Graduate Course in Computer Science

Copyleft @ 2019 Giuseppe Scollo

11 di 12

### references

recommended readings: Zwoliński, Ch. 4, Sect. 4.4-4.6

other sources for consultation: Harris, Harris, Ch. 4, Sect. 4.5, 4.8

useful materials for the proposed lab experience

(sources: DMI Library, Intel Corp. - FPGA University Program, 2016)

Tanenbaum: Structured computer organization, Fifth Edition (Pearson, 2006) Sect. 3.2.3 Making Qsys Components - For Quartus Prime 16.1, Appendix A Quartus Prime Introduction Using VHDL Designs - For Quartus Prime 16.1, Sect. 9 DE1-SoC Quartus Setting File with Pin Assignments

# VHDL sources:

examples in this presentation examples in Zwoliński book

DMI - Graduate Course in Computer Science

Copyleft @ 2019 Giuseppe Scollo